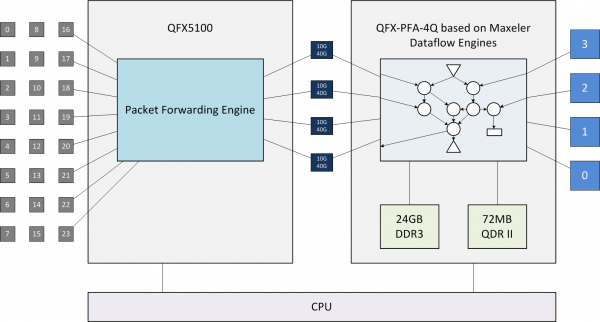

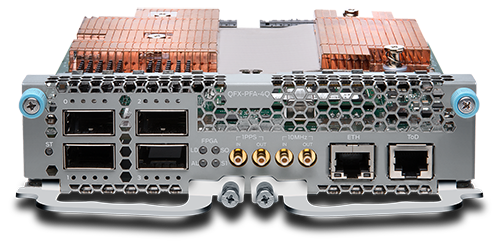

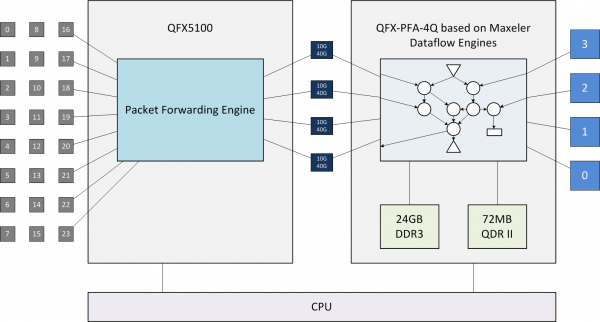

Juniper QFX5100 with QFX-PFA-4Q

QFX-PFA-4Q based on Maxeler Dataflow Engines

QFX5100 with QFX-PFA-4Q Module

System Diagram

Dataflow Computing: Programming in the data-plane

Software Defined Networking splits the control plane and the dataplane. Maxeler Dataflow computing makes the dataplane programmable. Dataflow computing focuses on optimizing the movement of data and utilizes massive parallelism from thousands of tiny ‘dataflow cores’ to provide 10-100x benefits in performance, space and power consumption.

The QFX-PFA-4Q is programmed using Maxeler’s dataflow compiler, including full TCP/IP support as well as a module to describe high level networking protocols in Java, to target the module. Network traffic can be decoded, transformed and re-encoded as a bump-in-the-wire, sustaining line rate throughputs with minimal, predictable and static latency.

Example Use Cases

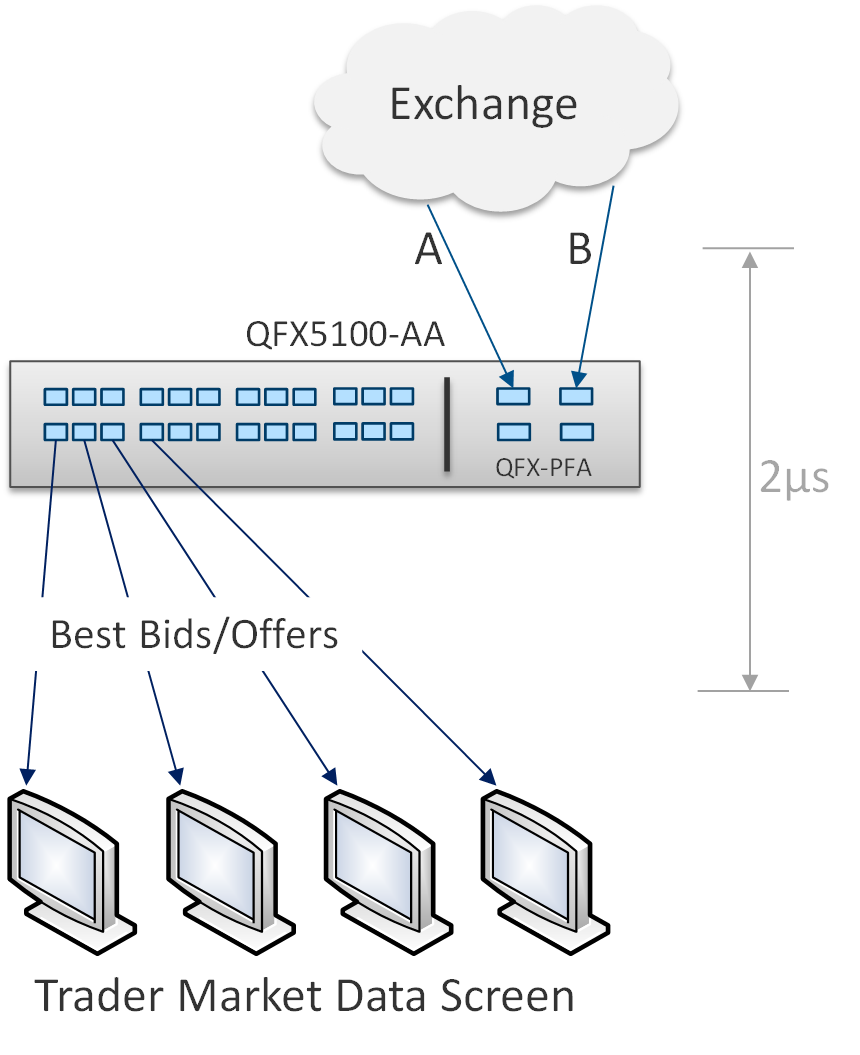

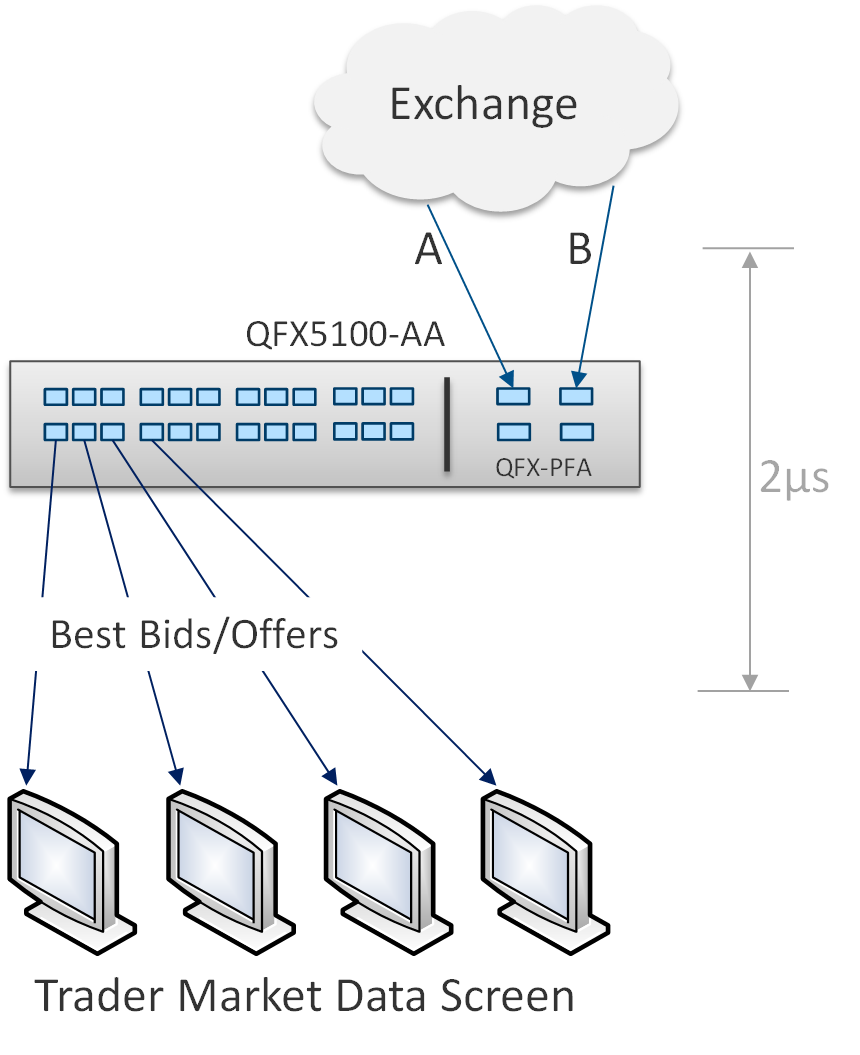

Exchange Market Data Distribution

- Market Data decoding and Order Book maintenance at full 10G line rate

- Supports native exchange protocols: FIX/FAST, ITCH, MDP 3.0 and more

- Multicasts the Top of Book – best prices to consumers

- Maintains multi-level order books for 1000s of instruments

- Arbitrates between redundant A/B Feeds

- Sub-2µs wire-to-wire latency

|

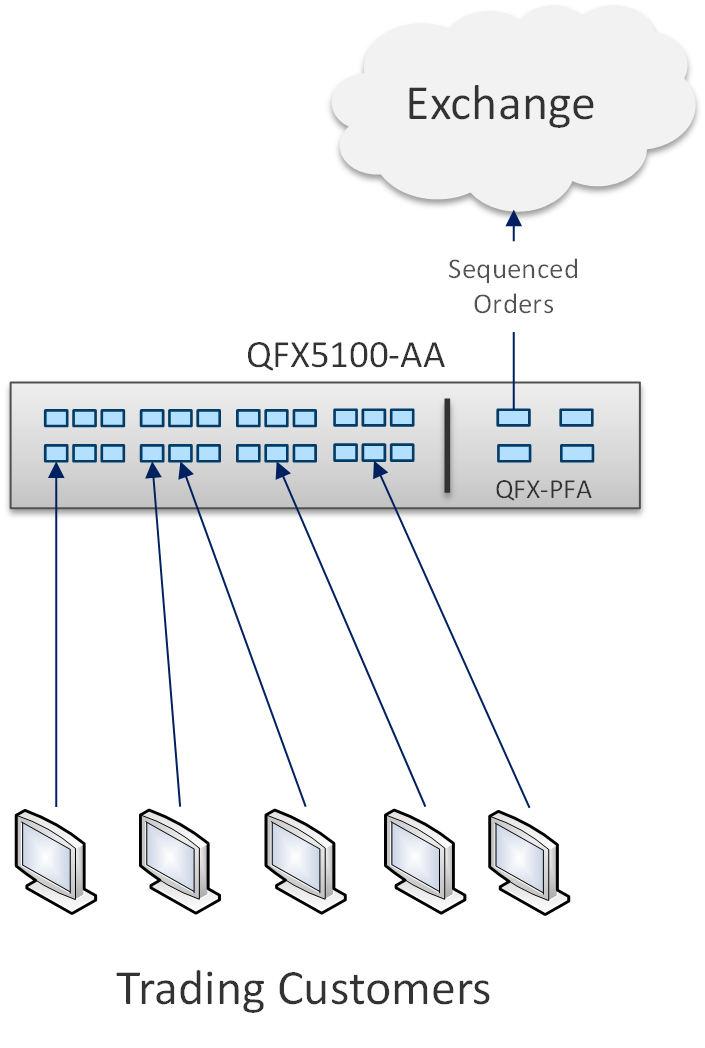

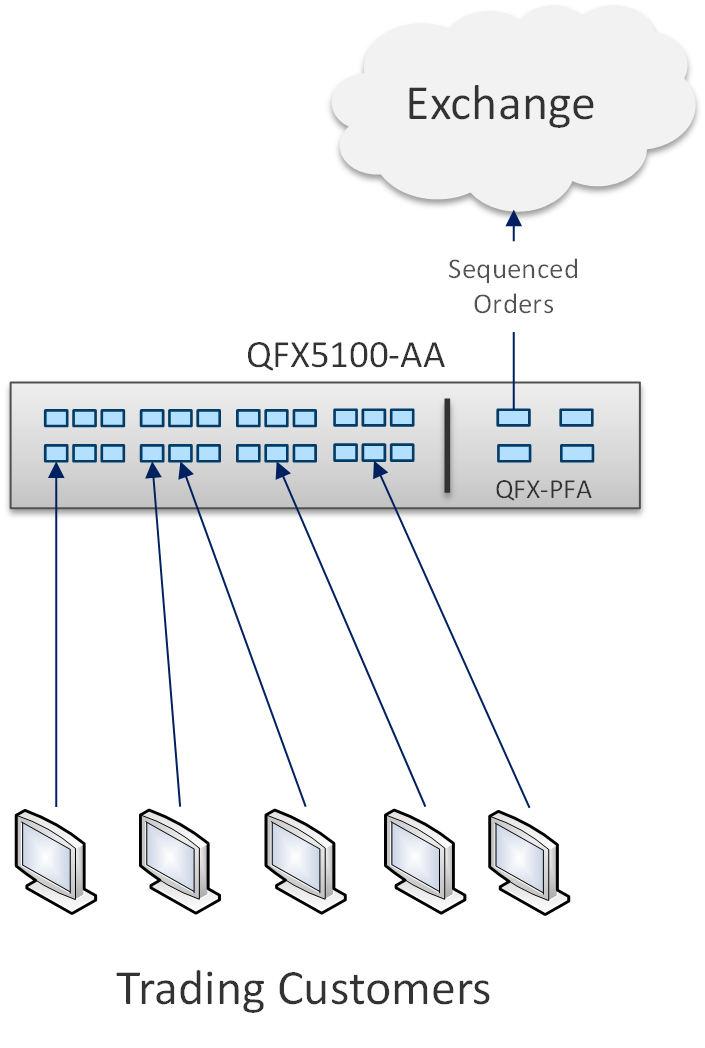

FIFO Order Gateway

- First-In, First Out – Order Sequencer

- Trading firms send their orders over a TCP connection

- All TCP connections get multiplexed into a single ordered stream – first complete message to come in is the first to leave the switch

- Support for 1000s of TCP connections

|

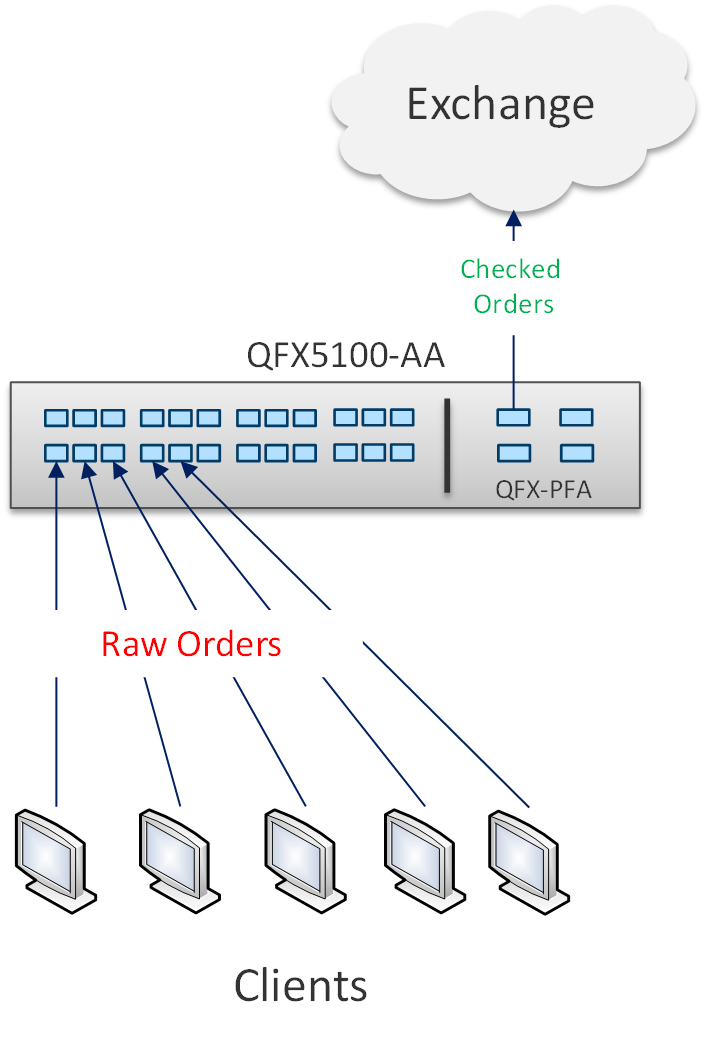

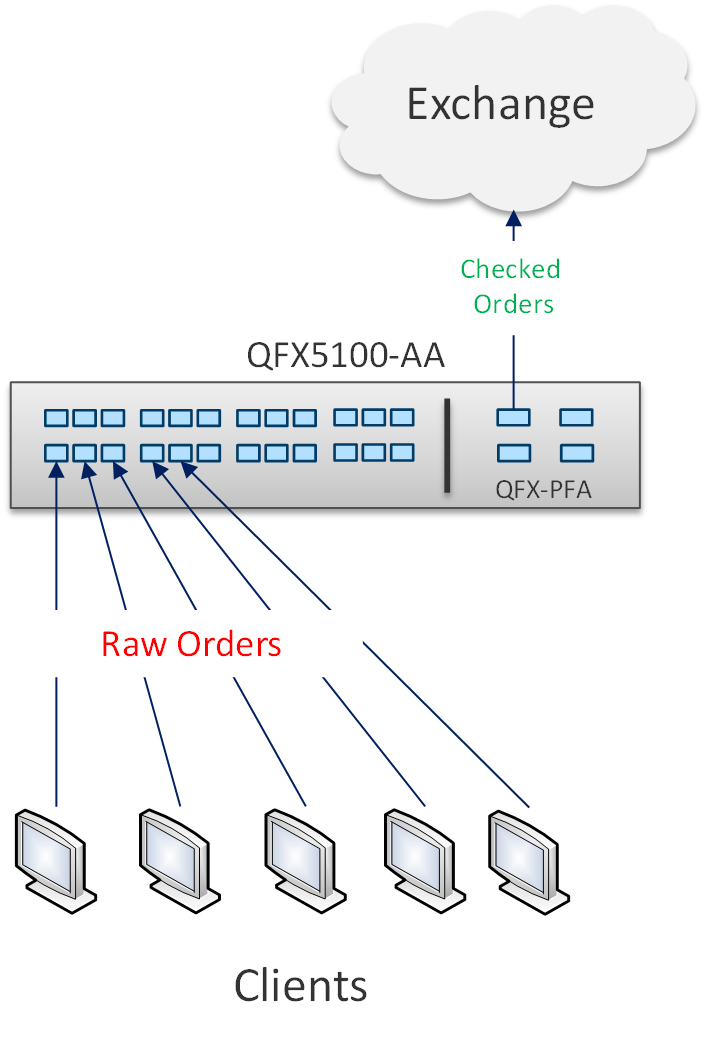

Pre-Trade Risk and Regulatory Compliance

-

Perform Pre-Trade Risk analysis on Order flow: eg. Position Limits

-

Comply with regulatory rules for eg. MiFID 2 – packet capture and time stamping

-

Full session maintenance

-

Encoding and Decoding of exchange native order entry protocols inside the switch

-

Extendable to many other types of pre-trade capabilities: eg. Speed bumps, Kill Switch etc

- Ultra-low latency and high throughput

|

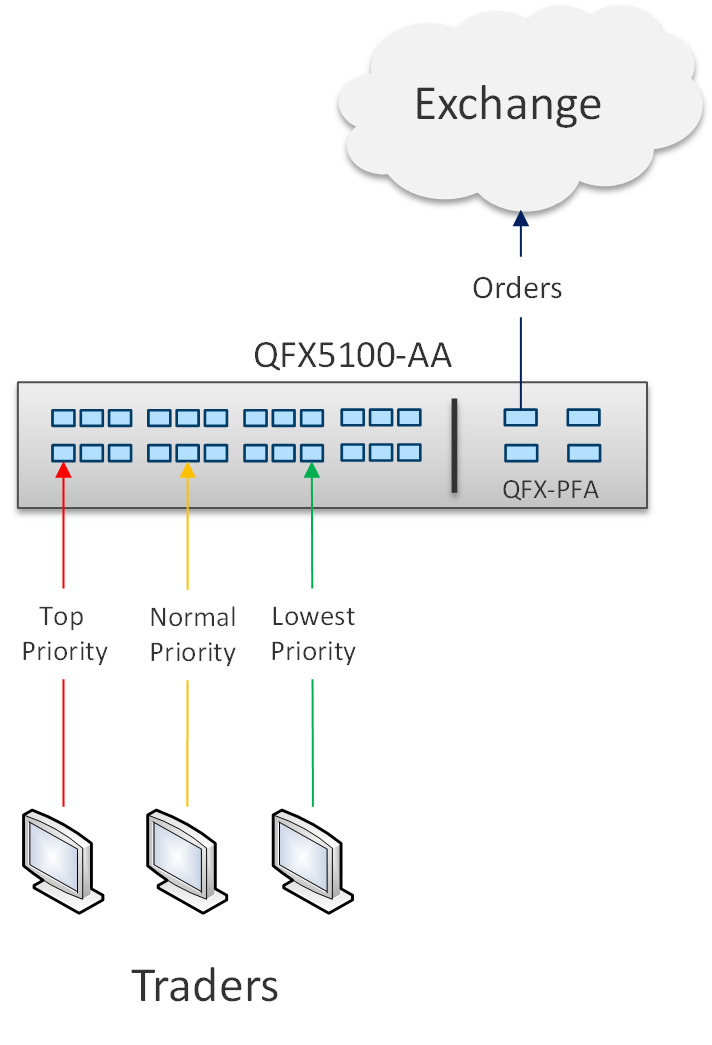

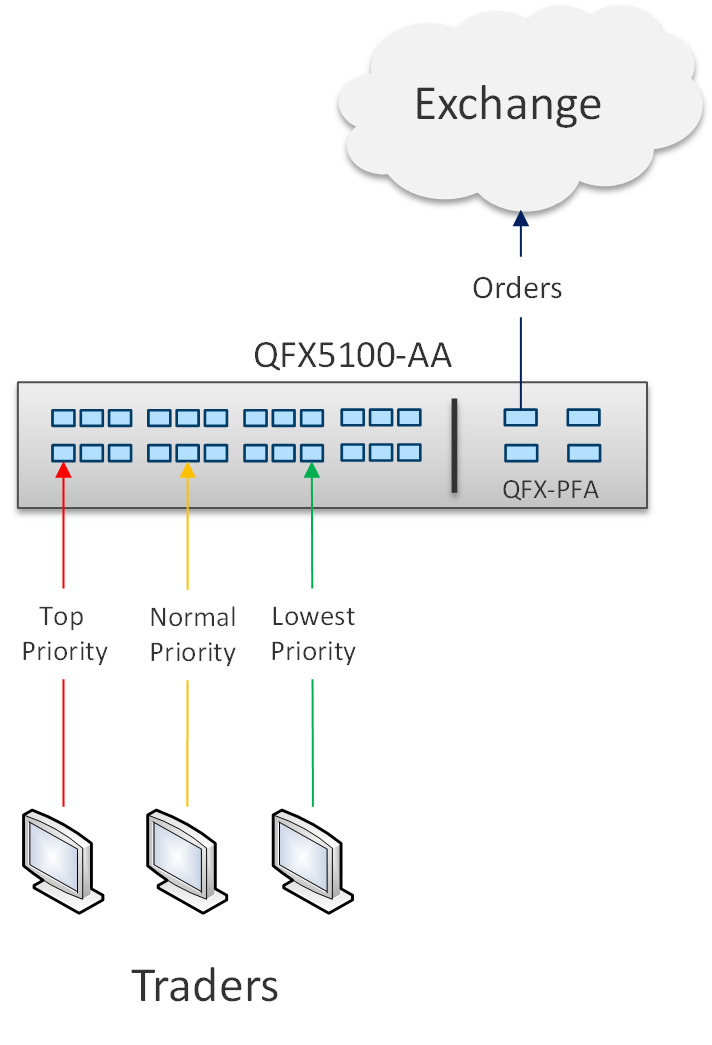

Order Entry Acceleration and Prioritization

-

Prioritizes between different orders on a shared line (eg. Hedge orders)

-

Accelerates order entry path by encoding the orders in to the FIX format over a TCP connection inside the switch

-

Orders come in using a binary format over a UDP connection

-

Allows multiple algos/users to share a single session

-

Multiple sessions supported

|

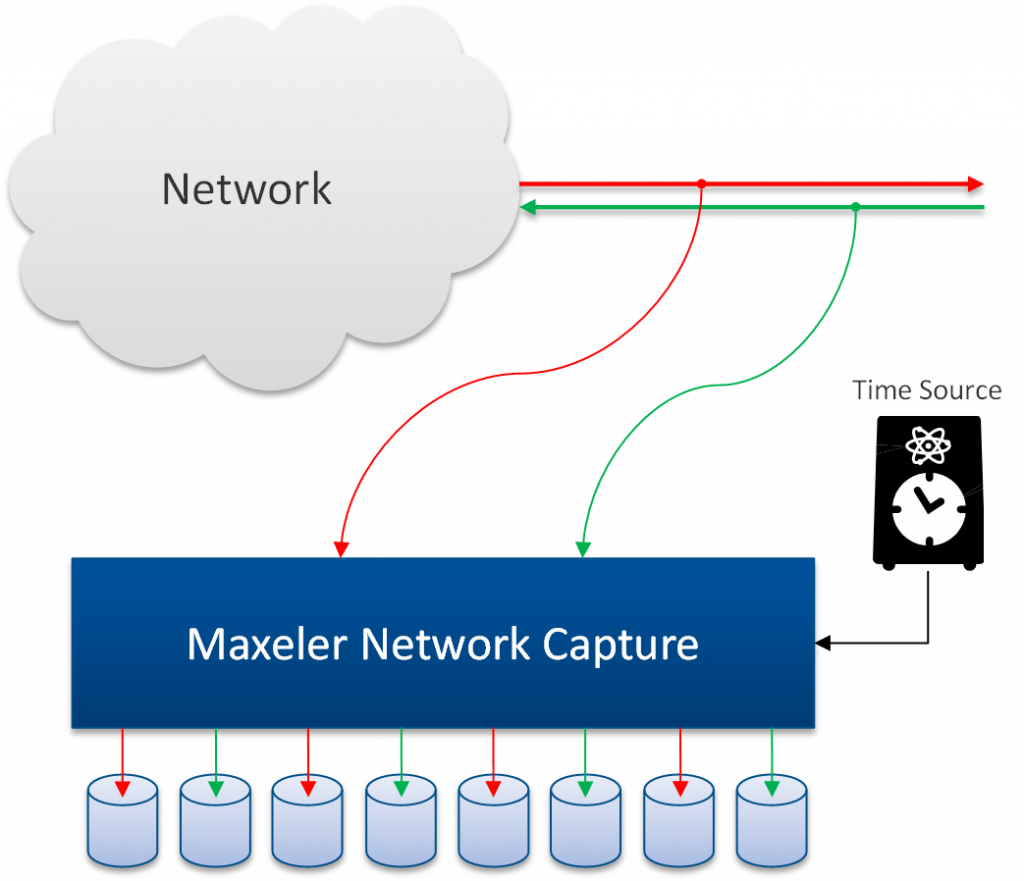

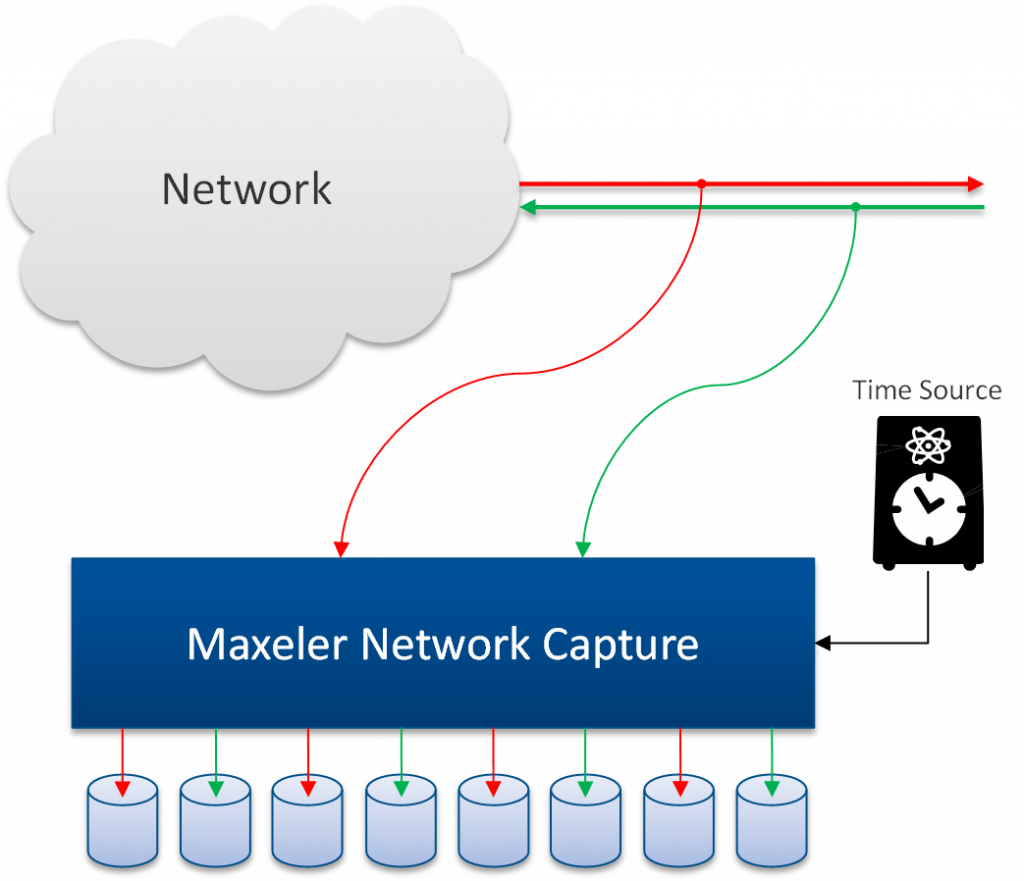

Network Packet Capture

- Provides sustained line-rate packet capture in distributed write mode and at bursts of up to 24GB in size in local write mode.

- Custom on-chip application layer (DPI) filtering and compression can be used to further reduce storage overhead and consolidate relevant data.

- The application configures pairs of DFE SFP ports into ‘tapped’ pass through connections. Ethernet data is captured from these ‘tapped’ connections and written out to pcap files.

- The DFE implementation sustains more reliable throughput than commodity software based packet capture solutions including deep packet filtering, distributed writing, and a large DRAM buffer.

|

VXLAN NAT Gateway

-

Decapsulate VXLAN packets

-

Validate the VM’s permissions to access the internet

-

Perform static NAT on the decapsulated flow

-

Runtime configurable – enable / disable specific VM’s internet access

-

Support 100K sessions on a single device

- Session: VXLAN VNI + Inner Source IP address

|

Custom Application

Custom application development is done using Maxeler’s MaxCompiler and library of IP blocks. Our reusable IP blocks include:

-

10G/40G Ethernet MAC

-

Hardware TCP Stack with support for up to 16K Connections

-

UDP/IP

-

Exchange Market Data decoders and Order Book Builders – ITCH, FIX/FAST, MDP3 for CME, Eurex, NASDAQ, and others

-

Exchange Order Execution – CME, Eurex, NASDAQ, etc

-

FIX Encoders / Decoders

-

High Accuracy Time Synchronization GPS / PTP

Contact Us

Please contact us for further inquiries.