MaxelerOS provides the data choreography needed to balance resources, maximize utilization, minimize overheads, and manage the application acceleration process at runtime.

MaxelerOS provides the data choreography needed to balance resources, maximize utilization, minimize overheads, and manage the application acceleration process at runtime.

MaxelerOS comprises both hardware and software. The hardware consists of components that form part of the FPGA configuration. The software running on the main processor interacts with MaxelerOS hardware over the interconnect, e.g., PCIe, Infiniband, FSB or Hypertransport.

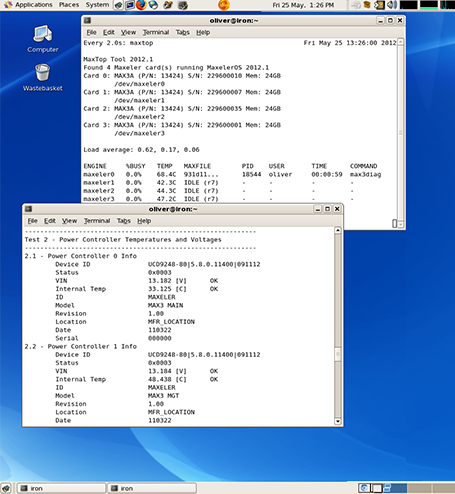

The MaxelerOS software interface provides the low-level interface between the application software and the DFE at run-time. It supports multiple DFEs per-node and running of all DFEs independently. Mutual-exclusion is enforced so that only one application can open a DFE at an instant. Streaming DMA in and out of the DFEs as well as interrupt based interraction are supported.

The MaxelerOS hardware blocks support data transfers: either single reads and writes or streaming. Dedicated interfaces are provided to ensure interoperability between blocks.